-

16CH LiDAR

SoC

SoC16CH LiDAR

- Time-to-Digital Converter for Time-of-Flight Applications

- Programmable Logic 내에서 AXI Bus Prototyping

- DDR3 Memory (4G-Bytes)x2 interface

- LD / APD 신호처리

- ToF 연산 – Floating Point

- 멀티코어 및 Object Detection

- Optimize boot speed

- Feature

- Zynq-7000

- Arm Cortex-A9 MPCore

- SPI, Gigabit Ethernet, CAN, UART, AXI Bus

- Boot emmc / SDcard

-

32CH LiDAR

SoC

SoC32CH LiDAR

- Time-to-Digital Converter for Time-of-Flight Applications

- Programmable Logic 내에서 AXI Bus Prototyping

- DDR3 Memory (4G-Bytes)x2 interface

- 고속 ADC Interface 및 신호처리 (Serdes)

- ToF 연산 – Floating Point

- 멀티코어 및 Object Detection

- Optimize boot speed

- Feature

- Zynq-7000

- Arm Cortex-A9 MPCore

- SPI, Gigabit Ethernet, CAN, UART, AXI Bus

- Boot emmc / SDcard

-

Drone LiDAR

SoC

SoCDrone LiDAR

- 16CH Lidar

- Time-to-Digital Converter for Time-of-Flight Applications

- ToF 연산 – Floating Point

- Feature

- Zynq-7000

- Arm Cortex-A9 MPCore

- Dual Processors 1GHz

- Boot Mode: Emmc / Micro SDcard / QSPI

- DDR3 8G Memory

- Gigabit Ethernet / USB port / USB2.0 / HDMI / JTAG

-

LiDAR Chip Verification Board

SoC

SoCLiDAR Chip Verification Board

- 16Ch Lidar

- LP / APD 신호처리

- ToF 연산 – Floating Point

- Feature

- Arm Cortex-A9 MPCore

- Dual Processors 1GHz

- DDR3 16G Memory

- Boot Mode: Emmc / Micro SDcard

- Gigabit Ethernet, JTAG, USB

-

ZynqMPSoC UltraScale+

SoC

SoCZynqMPSoC UltraScale+

- PS / PL 개발 환경 구축

- Petalinux 기반 Software 개발

- Verilog HDL/VHDL 기반 Logic 개발

- AXI Bus Prototyping

- Feature

- Dual Arm® Cortex®-A53

- Dual Processors 1GHz

- DDR3 16G Memory

- Boot Mode: Emmc / Micro SDcard

- Gigabit Ethernet, JTAG, USB

-

Line Laser

SoC

SoCLine Laser

- Gap&Flush 알고리즘 적용

- image processing 알고리즘 적용

- profile 변환 알고리즘 적용

- Feature

- Zynq-7000

- Arm Cortex-A9 MPCore

- Dual Processors 1GHz

- Boot Mode: Emmc / Micro SDcard / QSPI

- DDR3 8G Memory

- Gigabit Ethernet / USB port / USB2.0 / HDMI / JTAG

-

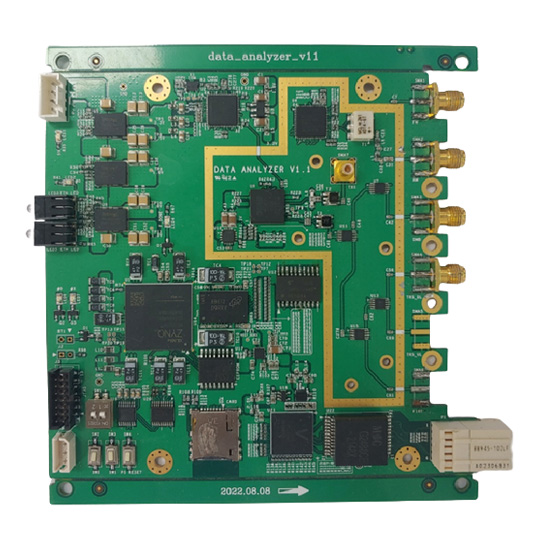

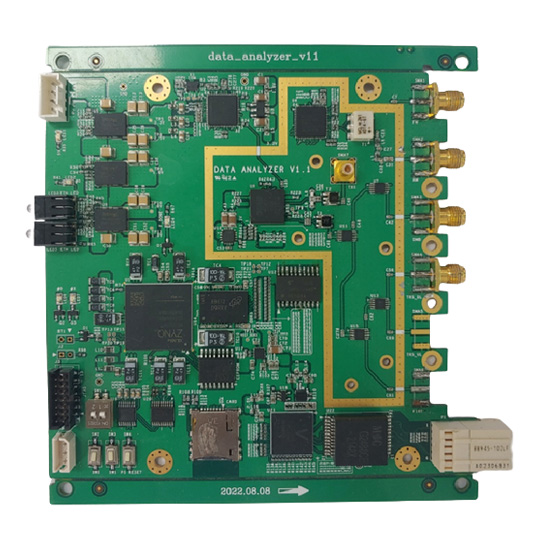

RF Analyzer

SoC

SoCRF Analyzer

- Radio frequency (RF) 2 x 2 transceiver with integrated

- Wide bandwidth: 325 MHz to 3.8 GHz

- Supports time division duplex (TDD) and frequency division duplex (FDD) operation

- Tunable channel bandwidth (BW): up to 20 MHz

- 12-bit DACs and ADCs

- 14-Output Clock Generator with Integrated 1.6 GHz VCO

- 14-Bit Dual Analog-to-Digital Converter

- Feature

- Zynq-7000

- Arm Cortex-A9 MPCore

- Dual Processors 1GHz

- Gigabit Ethernet, SPI, JTAG, UART, DMA

-

FMCW SAR ADC Module

SoC

SoCFMCW SAR ADC Module

- DAC 1CH

- ADC 2CH

- GPS Receiver

- SATA Interface & SSD 지원

- MAVLINK 지원

-

ADC Capture Board

SoC

SoCADC Capture Board

- DAC 2CH

- ADC 3CH

- GPS Receiver

- USB

- Giga ETH